Data Sheet

### December 27, 2004

# FN4324.2

# Buck and Synchronous-Rectifier Pulse-Width Modulator (PWM) Controller

intersil

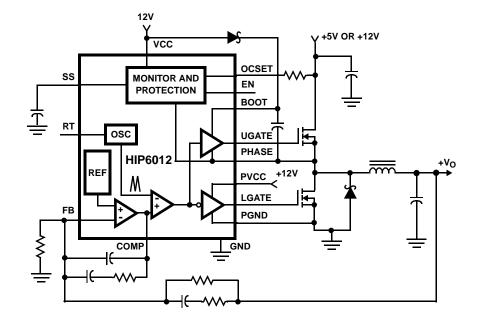

The HIP6012 provides complete control and protection for a DC-DC converter optimized for high-performance microprocessor applications. It is designed to drive two N-Channel MOSFETs in a synchronous-rectified buck topology. The HIP6012 integrates all of the control, output adjustment, monitoring and protection functions into a single package.

The output voltage of the converter can be precisely regulated to as low as 1.27V, with a maximum tolerance of  $\pm$ 1.5% over temperature and line voltage variations.

The HIP6012 provides simple, single feedback loop, voltagemode control with fast transient response. It includes a 200kHz free-running triangle-wave oscillator that is adjustable from below 50kHz to over 1MHz. The error amplifier features a 15MHz gain-bandwidth product and 6V/ $\mu$ s slew rate which enables high converter bandwidth for fast transient performance. The resulting PWM duty ratio ranges from 0% to 100%.

The HIP6012 protects against overcurrent conditions by inhibiting PWM operation. The HIP6012 monitors the current by using the  $r_{DS(ON)}$  of the upper MOSFET which eliminates the need for a current sensing resistor.

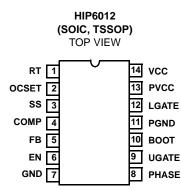

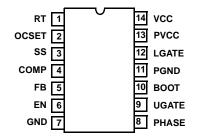

## Pinout

## Features

- Drives Two N-Channel MOSFETs

- Operates From +5V or +12V Input

- Simple Single-Loop Control Design

- Voltage-Mode PWM Control

- Fast Transient Response

- High-Bandwidth Error Amplifier

- Full 0% to 100% Duty Ratio

- Excellent Output Voltage Regulation

- 1.27V Internal Reference

- $\pm 1.5\%$  Over Line Voltage and Temperature

- Overcurrent Fault Monitor

- Does Not Require Extra Current Sensing Element

- Uses MOSFETs r<sub>DS(ON)</sub>

- Small Converter Size

- Constant Frequency Operation

- 200kHz Free-Running Oscillator Programmable from 50kHz to Over 1MHz

- 14 Pin, SOIC and TSSOP Packages

- Pb-Free Available (RoHS Compliant)

## Applications

- Power Supply for Pentium®, Pentium Pro, PowerPC<sup>™</sup> and Alpha<sup>™</sup> Microprocessors

- High-Power 5V to 3.xV DC-DC Regulators

- Low-Voltage Distributed Power Supplies

### **Ordering Information**

| PART<br>NUMBER           | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE               | PKG.<br>NO. |

|--------------------------|----------------------------------|-----------------------|-------------|

| HIP6012CB                | 0 to 70                          | 14 Ld SOIC            | M14.15      |

| HIP6012CBZ<br>(See Note) | 0 to 70                          | 14 Ld SOIC (Pb-free)  | M14.15      |

| HIP6012CV                | 0 to 70                          | 14 Ld TSSOP           | M14.173     |

| HIP6012CVZ<br>(See Note) | 0 to 70                          | 14 Ld TSSOP (Pb-free) | M14.173     |

Add "-T" suffix for tape and reel.

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

PowerPC<sup>™</sup> is a trademark of IBM. Alpha<sup>™</sup> is a trademark of Digital Equipment Corporation. Pentium® is a registered trademark of Intel Corporation.

# **Typical Application**

Block Diagram

#### **Absolute Maximum Ratings**

| Supply Voltage, V <sub>CC</sub> +15.0V                         |

|----------------------------------------------------------------|

| Boot Voltage, VBOOT - VPHASE + 15.0V                           |

| Input, Output or I/O VoltageGND -0.3V to V <sub>CC</sub> +0.3V |

| ESD Classification                                             |

### **Operating Conditions**

| Supply Voltage, V <sub>CC</sub> | . +12V ±10%                            |

|---------------------------------|----------------------------------------|

| Ambient Temperature Range       | $.0^{\circ}$ C to $70^{\circ}$ C       |

| Junction Temperature Range      | 0 <sup>o</sup> C to 125 <sup>o</sup> C |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)     | $\theta_{JA}$ (°C/W)                 |

|------------------------------------------|--------------------------------------|

| SOIC Package                             | 85                                   |

| TSSOP Package                            | 95                                   |

| Maximum Junction Temperature             |                                      |

| Maximum Storage Temperature Range        | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 10s) |                                      |

| (Lead tips only)                         |                                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

| PARAMETER                         | SYMBOL             | TEST CONDITIONS                                                       | MIN   | TYP   | MAX   | UNITS            |

|-----------------------------------|--------------------|-----------------------------------------------------------------------|-------|-------|-------|------------------|

| VCC SUPPLY CURRENT                |                    | 1                                                                     | 1     | 1     | I     |                  |

| Nominal Supply                    | ICC                | EN = V <sub>CC</sub> ; UGATE and LGATE Open                           | -     | 5     | -     | mA               |

| Shutdown Supply                   |                    | EN = 0V                                                               | -     | 50    | 100   | μA               |

| POWER-ON RESET                    |                    |                                                                       | 1     | 1     | I     |                  |

| Rising V <sub>CC</sub> Threshold  |                    | V <sub>OCSET</sub> = 4.5VDC                                           | -     | -     | 10.4  | V                |

| Falling V <sub>CC</sub> Threshold |                    | V <sub>OCSET</sub> = 4.5VDC                                           | 8.8   | -     | -     | V                |

| Enable - Input threshold Voltage  |                    | V <sub>OCSET</sub> = 4.5VDC                                           | 0.8   | -     | 2.0   | V                |

| Rising VOCSET Threshold           |                    |                                                                       | -     | 1.27  | -     | V                |

| OSCILLATOR                        | -                  |                                                                       | -+    | 1     | •     |                  |

| Free Running Frequency            |                    | $R_{T} = OPEN, V_{CC} = 12$                                           | 180   | 200   | 220   | kHz              |

| Total Variation                   |                    | $6k\Omega < R_T$ to GND < 200k $\Omega$                               | 2 -20 |       | +20   | %                |

| Ramp Amplitude                    | ∆V <sub>OSC</sub>  | R <sub>T</sub> = OPEN                                                 |       | 1.9   | -     | V <sub>P-P</sub> |

| REFERENCE                         |                    |                                                                       | - 1   | 1     | L     | 1                |

| Reference Voltage                 |                    |                                                                       | 1.251 | 1.270 | 1.289 | V                |

| ERROR AMPLIFIER                   | -                  |                                                                       | -+    | 1     | •     |                  |

| DC Gain                           |                    |                                                                       | -     | 88    | -     | dB               |

| Gain-Bandwidth Product            | GBW                |                                                                       | -     | 15    | -     | MHz              |

| Slew Rate                         | SR                 | COMP = 10pF                                                           | -     | 6     | -     | V/µs             |

| GATE DRIVERS                      | <b>I</b>           |                                                                       |       | 1     | L     | 1                |

| Upper Gate Source                 | IUGATE             | V <sub>BOOT</sub> - V <sub>PHASE</sub> = 12V, V <sub>UGATE</sub> = 6V | 350   | 500   | -     | mA               |

| Upper Gate Sink                   | R <sub>UGATE</sub> | I <sub>LGATE</sub> = 0.3A                                             | -     | 5.5   | 10    | W                |

| Lower Gate Source                 | ILGATE             | $V_{CC} = 12V, V_{LGATE} = 6V$                                        | 300   | 450   | -     | mA               |

| Lower Gate Sink                   | R <sub>LGATE</sub> | I <sub>LGATE</sub> = 0.3A                                             | -     | 3.5   | 6.5   | W                |

| PROTECTION                        | *                  | •                                                                     |       |       | •     |                  |

| OCSET Current Source              | IOCSET             | V <sub>OCSET</sub> = 4.5VDC                                           | 170   | 200   | 230   | μA               |

| Soft Start Current                | I <sub>SS</sub>    |                                                                       | -     | 10    | -     | μA               |

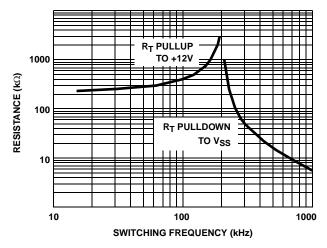

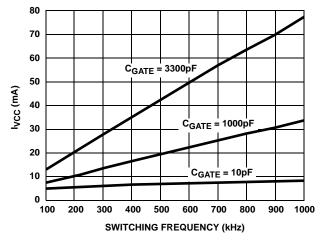

# Typical Performance Curves

FIGURE 1. RT RESISTANCE vs FREQUENCY

# Functional Pin Descriptions

# RT (Pin 1)

This pin provides oscillator switching frequency adjustment. By placing a resistor ( $R_T$ ) from this pin to GND, the nominal 200kHz switching frequency is increased according to the following equation:

$$Fs \approx 200 \text{ kHz} + \frac{5 \bullet 10^6}{R_T}$$

(R<sub>T</sub> to GND)

Conversely, connecting a pull-up resistor  $(R_T)$  from this pin to  $V_{CC}$  reduces the switching frequency according to the following equation.:

$$Fs \approx 200 \text{ kHz} - \frac{4 \bullet 10^7}{R_T}$$

(R<sub>T</sub> to 12V)

# OCSET (Pin 2)

Connect a resistor ( $R_{OCSET}$ ) from this pin to the drain of the upper MOSFET.  $R_{OCSET}$ , an internal 200 $\mu$ A current source ( $I_{OCS}$ ), and the upper MOSFET on-resistance ( $r_{DS(ON)}$ ) set the converter overcurrent (OC) trip point according to the following equation:

$$I_{\mathsf{PEAK}} = \frac{I_{\mathsf{OCS}} \bullet \mathsf{R}_{\mathsf{OCSET}}}{r_{\mathsf{DS}(\mathsf{ON})}}$$

FIGURE 2. BIAS SUPPLY CURRENT vs FREQUENCY

An overcurrent trip cycles the soft-start function.

## SS (Pin 3)

Connect a capacitor from this pin to ground. This capacitor, along with an internal  $10\mu A$  current source, sets the soft-start interval of the converter.

## COMP (Pin 4) and FB (Pin 5)

COMP and FB are the available external pins of the error amplifier. The FB pin is the inverting input of the error amplifier and the COMP pin is the error amplifier output. These pins are used to compensate the voltage-control feedback loop of the converter.

## EN (Pin 6)

This pin is the open-collector enable pin. Pull this pin below 1V to disable the converter. In shutdown, the soft start pin is discharged and the UGATE and LGATE pins are held low.

## GND (Pin 7)

Signal ground for the IC. All voltage levels are measured with respect to this pin.

## PHASE (Pin 8)

Connect the PHASE pin to the upper MOSFET source. This pin is used to monitor the voltage drop across the MOSFET for overcurrent protection. This pin also provides the return path for the upper gate drive.

### UGATE (Pin 9)

Connect UGATE to the upper MOSFET gate. This pin provides the gate drive for the upper MOSFET.

## BOOT (Pin 10)

This pin provides bias voltage to the upper MOSFET driver. A bootstrap circuit may be used to create a BOOT voltage suitable to drive a standard N-Channel MOSFET.

# PGND (Pin 11)

This is the power ground connection. Tie the lower MOSFET source to this pin.

# LGATE (Pin 12)

Connect LGATE to the lower MOSFET gate. This pin provides the gate drive for the lower MOSFET.

## PVCC (Pin 13)

Provide a bias supply for the lower gate drive to this pin.

## VCC (Pin 14)

Provide a 12V bias supply for the chip to this pin.

# Functional Description

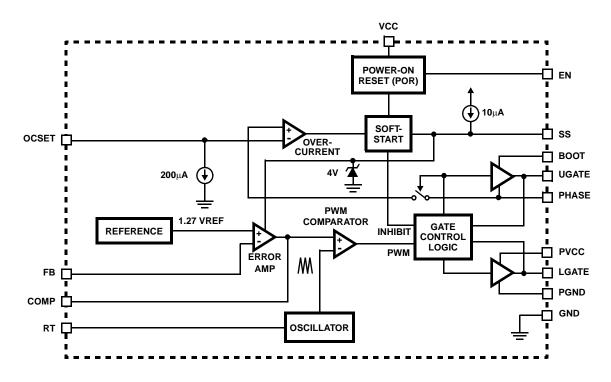

### Initialization

The HIP6012 automatically initializes upon receipt of power. Special sequencing of the input supplies is not necessary. The Power-On Reset (POR) function continually monitors the input supply voltages and the enable (EN) pin. The POR monitors the bias voltage at the VCC pin and the input voltage (V<sub>IN</sub>) on the OCSET pin. The level on OCSET is equal to V<sub>IN</sub> Less a fixed voltage drop (see overcurrent protection). With the EN pin held to V<sub>CC</sub>, the POR function initiates soft start operation after both input supply voltages exceed their POR thresholds. For operation with a single +12V power source, V<sub>IN</sub> and V<sub>CC</sub> are equivalent and the +12V power source must exceed the rising V<sub>CC</sub> threshold before POR initiates operation.

The Power-On Reset (POR) function inhibits operation with the chip disabled (EN pin low). With both input supplies above their POR thresholds, transitioning the EN pin high initiates a soft start interval.

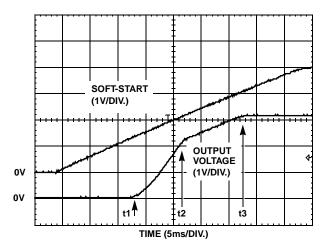

## Soft Start

The POR function initiates the soft start sequence. An internal 10µA current source charges an external capacitor (CSS) on the SS pin to 4V. Soft start clamps the error amplifier output (COMP pin) and reference input (+ terminal of error amp) to the SS pin voltage. Figure 3 shows the soft start interval with  $C_{SS} = 0.1 \mu F$ . Initially the clamp on the error amplifier (COMP pin) controls the converter's output voltage. At t1 in Figure 3, the SS voltage reaches the valley of the oscillator's triangle wave. The oscillator's triangular waveform is compared to the ramping error amplifier voltage. This generates PHASE pulses of increasing width that charge the output capacitor(s). This interval of increasing pulse width continues to t2. With sufficient output voltage, the clamp on the reference input controls the output voltage. This is the interval between t2 and t3 in Figure 3. At t3 the SS voltage exceeds the reference voltage and the output voltage is in regulation. This method provides a rapid and controlled output voltage rise.

FIGURE 3. SOFT-START INTERVAL

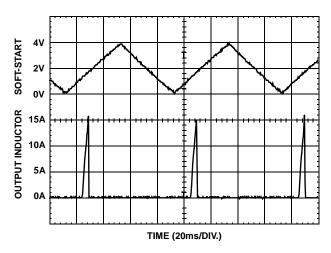

FIGURE 4. OVERCURRENT OPERATION

# **Overcurrent Protection**

The overcurrent function protects the converter from a shorted output by using the upper MOSFETs on-resistance,  $r_{DS(ON)}$  to monitor the current. This method enhances the converter's efficiency and reduces cost by eliminating a current sensing resistor.

The overcurrent function cycles the soft-start function in a hiccup mode to provide fault protection. A resistor (R<sub>OCSET</sub>) programs the overcurrent trip level. An internal 200µA (typical) current sink develops a voltage across R<sub>OCSET</sub> that is reference to V<sub>IN</sub>. When the voltage across the upper MOSFET (also referenced to V<sub>IN</sub>) exceeds the voltage across R<sub>OCSET</sub>, the overcurrent function initiates a soft-start sequence. The soft-start function discharges C<sub>SS</sub> with a 10µA current sink and inhibits PWM operation. The soft-start function recharges C<sub>SS</sub>, and PWM operation resumes with the error amplifier clamped to the SS voltage. Should an overload occur while recharging C<sub>SS</sub>, the soft start function inhibits PWM operation while fully charging C<sub>SS</sub> to 4V to

complete its cycle. Figure 4 shows this operation with an overload condition. Note that the inductor current increases to over 15A during the  $C_{SS}$  charging interval and causes an overcurrent trip. The converter dissipates very little power with this method. The measured input power for the conditions of Figure 4 is 2.5W.

The overcurrent function will trip at a peak inductor current  $(\mathsf{I}_{\mathsf{PEAK}})$  determined by:

$$I_{\mathsf{PEAK}} = \frac{I_{\mathsf{OCSET}} \bullet \mathsf{R}_{\mathsf{OCSET}}}{r_{\mathsf{DS}(\mathsf{ON})}}$$

where  $I_{OCSET}$  is the internal OCSET current source  $(200\mu A$ - typical). The OC trip point varies mainly due to the MOSFETs  $r_{DS(ON)}$  variations. To avoid overcurrent tripping in the normal operating load range, find the  $R_{OCSET}$  resistor from the equation above with:

- 1. The maximum  $r_{DS(ON)}$  at the highest junction temperature.

- 2. The minimum  $I_{OCSET}$  from the specification table.

- 3. Determine  $I_{PEAK}$  for  $I_{PEAK} > I_{OUT(MAX)} + (\Delta I)/2$  , where  $\Delta I$  is the output inductor ripple current.

For an equation for the ripple current see the section under component guidelines titled 'Output Inductor Selection'.

A small ceramic capacitor should be placed in parallel with  $R_{OCSET}$  to smooth the voltage across  $R_{OCSET}$  in the presence of switching noise on the input voltage.

# Application Guidelines

### Layout Considerations

As in any high frequency switching converter, layout is very important. Switching current from one power device to another can generate voltage transients across the impedances of the interconnecting bond wires and circuit traces. These interconnecting impedances should be minimized by using wide, short printed circuit traces. The critical components should be located as close together as possible using ground plane construction or single point grounding.

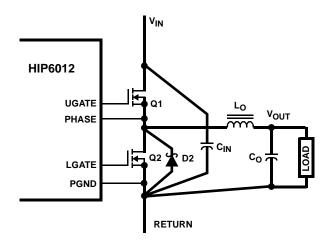

Figure 5 shows the critical power components of the converter. To minimize the voltage overshoot the interconnecting wires indicated by heavy lines should be part of ground or power plane in a printed circuit board. The components shown in Figure 6 should be located as close together as possible. Please note that the capacitors  $C_{IN}$  and  $C_O$  each represent numerous physical capacitors. Locate the HIP6012 within 3 inches of the MOSFETs, Q1 and Q2. The circuit traces for the MOSFETs' gate and source connections from the HIP6012 must be sized to handle up to 1A peak current.

Figure 6 shows the circuit traces that require additional layout consideration. Use single point and ground plane construction for the circuits shown. Minimize any leakage current paths on the SS PIN and locate the capacitor,  $C_{SS}$

close to the SS pin because the internal current source is only 10 $\mu$ A. Provide local V<sub>CC</sub> decoupling between VCC and GND pins. Locate the capacitor, C<sub>BOOT</sub> as close as practical to the BOOT and PHASE pins.

#### FIGURE 5. PRINTED CIRCUIT BOARD POWER AND GROUND PLANES OR ISLANDS

FIGURE 6. PRINTED CIRCUIT BOARD SMALL SIGNAL LAYOUT GUIDELINES

### Feedback Compensation

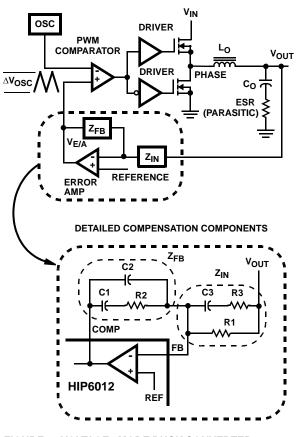

Figure 7 highlights the voltage-mode control loop for a synchronous-rectified buck converter. The output voltage  $(V_{OUT})$  is regulated to the Reference voltage level. The error amplifier (Error Amp) output  $(V_{E/A})$  is compared with the oscillator (OSC) triangular wave to provide a pulse-width modulated (PWM) wave with an amplitude of  $V_{IN}$  at the PHASE node. The PWM wave is smoothed by the output filter (L<sub>O</sub> and C<sub>O</sub>).

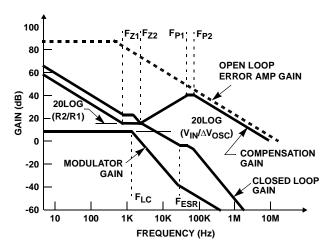

The modulator transfer function is the small-signal transfer function of V<sub>OUT</sub>/V<sub>E/A</sub>. This function is dominated by a DC Gain and the output filter (L<sub>O</sub> and C<sub>O</sub>), with a double pole break frequency at F<sub>LC</sub> and a zero at F<sub>ESR</sub>. The DC Gain of the modulator is simply the input voltage (V<sub>IN</sub>) Divided by the peak-to-peak oscillator voltage  $\Delta V_{OSC}$ .

FIGURE 7. VOLTAGE - MODE BUCK CONVERTER COMPENSATION DESIGN

### Modulator Break Frequency Equations

$$F_{LC} = \frac{1}{2\pi \bullet \sqrt{L_0 \bullet C_0}} \qquad F_{ESR} = \frac{1}{2\pi \bullet (ESR \bullet C_0)}$$

The compensation network consists of the error amplifier (internal to the HIP6012) and the impedance networks  $Z_{IN}$  and  $Z_{FB}$ . The goal of the compensation network is to provide a closed loop transfer function with the highest 0dB crossing frequency ( $f_{0dB}$ ) and adequate phase margin. Phase margin is the difference between the closed loop phase at  $f_{0dB}$  and  $180^{\circ}$ . The equations below relate the compensation network's poles, zeros and gain to the components (R1, R2, R3, C1, C2, and C3) in Figure 8. Use these guidelines for locating the poles and zeros of the compensation network:

### **Compensation Break Frequency Equations**

$$F_{Z1} = \frac{1}{2\pi \bullet R2 \bullet C1}$$

$$F_{P1} = \frac{1}{2\pi \bullet R2 \bullet \left(\frac{C1 \bullet C2}{C1 + C2}\right)}$$

$$F_{Z2} = \frac{1}{2\pi \bullet (R1 + R3) \bullet C3}$$

$$F_{P2} = \frac{1}{2\pi \bullet R3 \bullet C3}$$

1. Pick Gain (R2/R1) for desired converter bandwidth

7

- 2. Place 1<sup>ST</sup> Zero Below Filter's Double Pole (~75% F<sub>LC</sub>)

- 3. Place 2<sup>ND</sup> Zero at Filter's Double Pole

- 4. Place  $1^{ST}$  Pole at the ESR Zero

- 5. Place 2<sup>ND</sup> Pole at Half the Switching Frequency

- 6. Check Gain against Error Amplifier's Open-Loop Gain

- 7. Estimate Phase Margin Repeat if Necessary

Figure 8 shows an asymptotic plot of the DC-DC converter's gain vs frequency. The actual Modulator Gain has a high gain peak do to the high Q factor of the output filter and is not shown in Figure 8. Using the above guidelines should give a Compensation Gain similar to the curve plotted. The open loop error amplifier gain bounds the compensation gain. Check the compensation gain at  $F_{P2}$  with the capabilities of the error amplifier. The Closed Loop Gain is constructed on the log-log graph of Figure 8 by adding the Modulator Gain (in dB) to the Compensation Gain (in dB). This is equivalent to multiplying the modulator transfer function to the compensation transfer function and plotting the gain.

#### FIGURE 8. ASYMPTOTIC BODE PLOT OF CONVERTER GAIN

The compensation gain uses external impedance networks  $Z_{FB}$  and  $Z_{IN}$  to provide a stable, high bandwidth (BW) overall loop. A stable control loop has a gain crossing with -20dB/decade slope and a phase margin greater than 45<sup>o</sup>. Include worst case component variations when determining phase margin.

## **Component Selection Guidelines**

### **Output Capacitor Selection**

An output capacitor is required to filter the output and supply the load transient current. The filtering requirements are a function of the switching frequency and the ripple current. The load transient requirements are a function of the slew rate (di/dt) and the magnitude of the transient load current. These requirements are generally met with a mix of capacitors and careful layout.

Modern microprocessors produce transient load rates above 1A/ns. High frequency capacitors initially supply the transient and slow the current load rate seen by the bulk capacitors. The bulk filter capacitor values are generally determined by the ESR (effective series resistance) and voltage rating requirements rather than actual capacitance requirements. High frequency decoupling capacitors should be placed as close to the power pins of the load as physically possible. Be careful not to add inductance in the circuit board wiring that could cancel the usefulness of these low inductance components. Consult with the manufacturer of the load on specific decoupling requirements. For example, Intel recommends that the high frequency decoupling for the Pentium-Pro be composed of at least forty (40)  $1.0\mu$ F ceramic capacitors in the 1206 surface-mount package.

Use only specialized low-ESR capacitors intended for switching-regulator applications for the bulk capacitors. The bulk capacitor's ESR will determine the output ripple voltage and the initial voltage drop after a high slew-rate transient. An aluminum electrolytic capacitor's ESR value is related to the case size with lower ESR available in larger case sizes. However, the equivalent series inductance (ESL) of these capacitors increases with case size and can reduce the usefulness of the capacitor to high slew-rate transient loading. Unfortunately, ESL is not a specified parameter. Work with your capacitor supplier and measure the capacitor's impedance with frequency to select a suitable component. In most cases, multiple electrolytic capacitors of small case size perform better than a single large case capacitor.

#### **Output Inductor Selection**

The output inductor is selected to meet the output voltage ripple requirements and minimize the converter's response time to the load transient. The inductor value determines the converter's ripple current and the ripple voltage is a function of the ripple current. The ripple voltage and current are approximated by the following equations:

$$\Delta I = \frac{V_{IN} - V_{OUT}}{F_{S \times L}} \bullet \frac{V_{OUT}}{V_{IN}} \qquad \Delta V_{OUT} = \Delta I \times ESR$$

Increasing the value of inductance reduces the ripple current and voltage. However, the large inductance values reduce the converter's response time to a load transient.

One of the parameters limiting the converter's response to a load transient is the time required to change the inductor current. Given a sufficiently fast control loop design, the HIP6012 will provide either 0% or 100% duty cycle in response to a load transient. The response time is the time required to slew the inductor current from an initial current value to the transient current level. During this interval the difference between the inductor current and the transient current level must be supplied by the output capacitor. Minimizing the response time can minimize the output capacitance required.

The response time to a transient is different for the application of load and the removal of load. The following equations give the approximate response time interval for application and removal of a transient load:

$$t_{\text{RISE}} = \frac{L_{\text{O}} \times I_{\text{TRAN}}}{V_{\text{IN}} - V_{\text{OUT}}} \qquad t_{\text{FALL}} = \frac{L_{\text{O}} \times I_{\text{TRAN}}}{V_{\text{OUT}}}$$

where:  $I_{TRAN}$  is the transient load current step,  $t_{RISE}$  is the response time to the application of load, and  $t_{FALL}$  is the response time to the removal of load. With a +5V input source, the worst case response time can be either at the application or removal of load and dependent upon the output voltage setting. Be sure to check both of these equations at the minimum and maximum output levels for the worst case response time.

#### Input Capacitor Selection

Use a mix of input bypass capacitors to control the voltage overshoot across the MOSFETs. Use small ceramic capacitors for high frequency decoupling and bulk capacitors to supply the current needed each time Q1 turns on. Place the small ceramic capacitors physically close to the MOSFETs and between the drain of Q1 and the source of Q2.

The important parameters for the bulk input capacitor are the voltage rating and the RMS current rating. For reliable operation, select the bulk capacitor with voltage and current ratings above the maximum input voltage and largest RMS current required by the circuit. The capacitor voltage rating should be at least 1.25 times greater than the maximum input voltage and a voltage rating of 1.5 times is a conservative guideline. The RMS current rating requirement for the input capacitor of a buck regulator is approximately 1/2 the DC load current.

For a through hole design, several electrolytic capacitors (Panasonic HFQ series or Nichicon PL series or Sanyo MV-GX or equivalent) may be needed. For surface mount designs, solid tantalum capacitors can be used, but caution must be exercised with regard to the capacitor surge current rating. These capacitors must be capable of handling the surge-current at power-up. The TPS series available from AVX, and the 593D series from Sprague are both surge current tested.

### **MOSFET Selection/Considerations**

The HIP6012 requires 2 N-Channel power MOSFETs. These should be selected based upon r<sub>DS(ON)</sub>, gate supply requirements, and thermal management requirements.

In high-current applications, the MOSFET power dissipation, package selection and heatsink are the dominant design factors. The power dissipation includes two loss components; conduction loss and switching loss. The conduction losses are the largest component of power dissipation for both the upper and the lower MOSFETs. These losses are distributed between the two MOSFETs according to duty factor (see the equations below). Only the upper MOSFET has switching losses, since the Schottky rectifier clamps the switching node before the synchronous rectifier turns on.

$$\begin{split} \mathsf{P}_{\mathsf{UPPER}} &= \mathsf{I}_O{}^2 \times \mathsf{r}_{\mathsf{DS}(\mathsf{ON})} \times \mathsf{D} + \qquad \frac{1}{2} \; \mathsf{lo} \times \mathsf{V}_{\mathsf{IN}} \times \mathsf{t}_{\mathsf{SW}} \times \mathsf{Fs} \\ \mathsf{P}_{\mathsf{LOWER}} &= \mathsf{I}_O{}^2 \times \mathsf{r}_{\mathsf{DS}(\mathsf{ON})} \times (1 - \mathsf{D}) \end{split}$$

Where: D is the duty cycle = V<sub>O</sub> / V<sub>IN</sub>,  $\mathsf{t}_{\mathsf{SW}}$  is the switching interval, and Fs is the switching frequency. These equations assume linear voltage-current transitions and do not adequately model power loss due the reverserecovery of the lower MOSFETs body diode. The gate-charge losses are dissipated by the HIP6012 and don't heat the MOSFETs. However, large gate-charge increases the switching interval,  $t_{SW}$  which increases the upper MOSFET switching losses. Ensure that both MOSFETs are within their maximum junction temperature at high ambient temperature by calculating the temperature rise according to package thermal-resistance specifications. A separate heatsink may be necessary depending upon MOSFET power, package type, ambient temperature and air flow.

Standard-gate MOSFETs are normally recommended for use with the HIP6012. However, logic-level gate MOSFETs can be used under special circumstances. The input voltage, upper gate drive level, and the MOSFETs absolute gate-tosource voltage rating determine whether logic-level MOSFETs are appropriate.

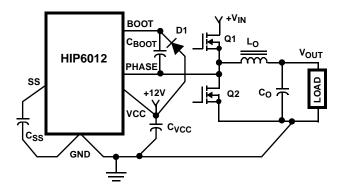

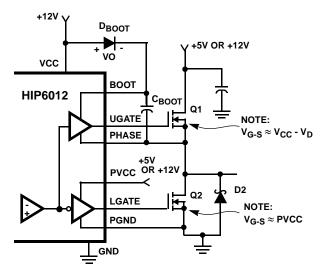

Figure 9 shows the upper gate drive (BOOT pin) supplied by a bootstrap circuit from V<sub>CC</sub>. The boot capacitor, C<sub>BOOT</sub> develops a floating supply voltage referenced to the PHASE pin. This supply is refreshed each cycle to a voltage of V<sub>CC</sub> less the boot diode drop (V<sub>D</sub>) when the lower MOSFET, Q2 turns on. A logic-level MOSFET can only be used for Q1 if the MOSFETs absolute gate-to-source voltage rating exceeds the maximum voltage applied to V<sub>CC</sub>. For Q2, a logic-level MOSFET can be used if its absolute gate-to-source voltage rating exceeds the maximum voltage applied to V<sub>CC</sub>.

FIGURE 9. UPPER GATE DRIVE - BOOTSTRAP OPTION

9

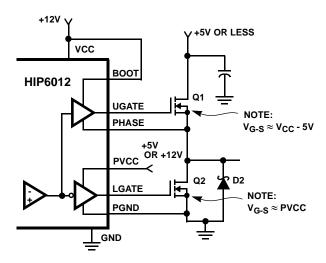

Figure 10 shows the upper gate drive supplied by a direct connection to  $V_{CC}$ . This option should only be used in converter systems where the main input voltage is +5 VDC or less. The peak upper gate-to-source voltage is approximately VCC less the input supply. For +5V main power and +12 VDC for the bias, the gate-to-source voltage of Q1 is 7V. A logic-level MOSFET is a good choice for Q1 and a logic-level MOSFET can be used for Q2 if its absolute gate-to-source voltage rating exceeds the maximum voltage applied to PVCC.

FIGURE 10. UPPER GATE DRIVE - DIRECT V<sub>CC</sub> DRIVE OPTION

### Schottky Selection

Rectifier D2 is a clamp that catches the negative inductor swing during the dead time between turning off the lower MOSFET and turning on the upper MOSFET. The diode must be a Schottky type to prevent the lossy parasitic MOSFET body diode from conducting. It is acceptable to omit the diode and let the body diode of the lower MOSFET clamp the negative inductor swing, but efficiency will drop one or two percent as a result. The diode's rated reverse breakdown voltage must be greater than the maximum input voltage.

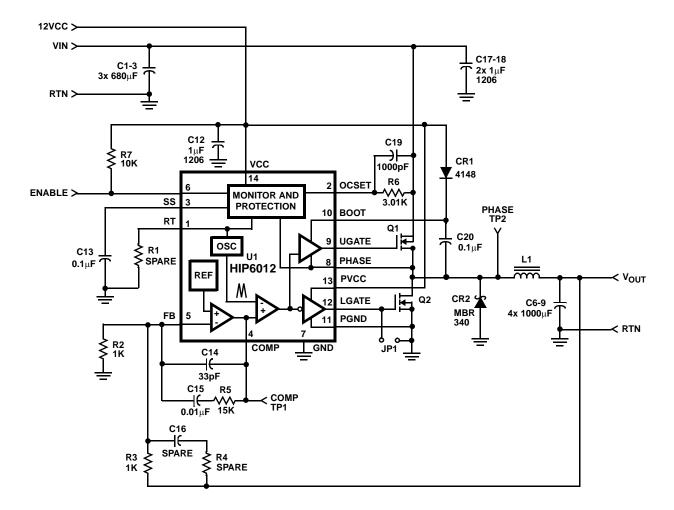

# HIP6012 DC-DC Converter Application Circuit

The figure below shows a DC-DC converter circuit for a microprocessor application, originally designed to employ the HIP6006 controller. Given the similarities between the HIP6006 and HIP6012 controllers, the circuit can be implemented using the HIP6012 controller without any modifications. However, given the expanded reference

voltage tolerance range, the HIP6012-based converter may require additional output capacitance. Detailed information on the circuit, including a complete Bill-of-Materials and circuit board description, can be found in application note AN9722. See Intersil's home page on the web: www.intersil.com

Component Selection Notes:

- C1-C3  $\,$  -3 each 680  $\mu F$  25W VDC, Sanyo MV-GX or equivalent.

- C6-C9 -4 each 1000µF 6.3W VDC, Sanyo MV-GX or equivalent.

- L1 -Core: Micrometals T50-52B; Winding: 10 Turns of 17AWG.

- CR1 -1N4148 or equivalent.

- CR2 -3A, 40V Schottky, Motorola MBR340 or equivalent.

- Q1, Q2 -Intersil MOSFET; RFP25N05

#### FIGURE 11. DC-DC CONVERTER APPLICATION CIRCUIT

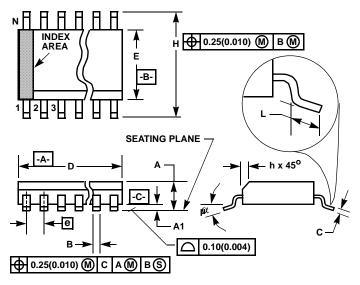

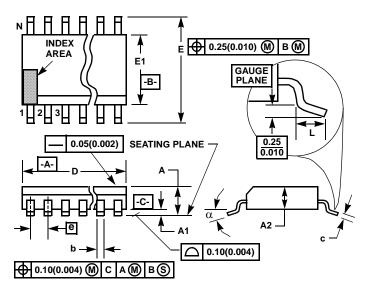

# Small Outline Plastic Packages (SOIC)

#### NOTES:

- 1. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- 4. Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- 9. The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- 10. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

#### M14.15 (JEDEC MS-012-AB ISSUE C) 14 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INCHES         |                | MILLIMETERS    |                |       |

|--------|----------------|----------------|----------------|----------------|-------|

| SYMBOL | MIN            | MAX            | MIN            | MAX            | NOTES |

| А      | 0.0532         | 0.0688         | 1.35           | 1.75           | -     |

| A1     | 0.0040         | 0.0098         | 0.10           | 0.25           | -     |

| В      | 0.013          | 0.020          | 0.33           | 0.51           | 9     |

| С      | 0.0075         | 0.0098         | 0.19           | 0.25           | -     |

| D      | 0.3367         | 0.3444         | 8.55           | 8.75           | 3     |

| E      | 0.1497         | 0.1574         | 3.80           | 4.00           | 4     |

| е      | 0.050 BSC      |                | 1.27 BSC       |                | -     |

| Н      | 0.2284         | 0.2440         | 5.80           | 6.20           | -     |

| h      | 0.0099         | 0.0196         | 0.25           | 0.50           | 5     |

| L      | 0.016          | 0.050          | 0.40           | 1.27           | 6     |

| Ν      | 14             |                | 14             |                | 7     |

| α      | 0 <sup>0</sup> | 8 <sup>0</sup> | 0 <sup>0</sup> | 8 <sup>0</sup> | -     |

Rev. 0 12/93

# Thin Shrink Small Outline Plastic Packages (TSSOP)

#### NOTES:

- 1. These package dimensions are within allowable dimensions of JEDEC MO-153-AC, Issue E.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E1" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.15mm (0.006 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- 9. Dimension "b" does not include dambar protrusion. Allowable dambar protrusion shall be 0.08mm (0.003 inch) total in excess of "b" dimension at maximum material condition. Minimum space between protrusion and adjacent lead is 0.07mm (0.0027 inch).

- 10. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact. (Angles in degrees)

#### M14.173

14 LEAD THIN SHRINK SMALL OUTLINE PLASTIC PACKAGE

|        | INCHES         |                | MILLIMETERS    |                |       |

|--------|----------------|----------------|----------------|----------------|-------|

| SYMBOL | MIN            | MAX            | MIN            | MAX            | NOTES |

| А      | -              | 0.047          | -              | 1.20           | -     |

| A1     | 0.002          | 0.006          | 0.05           | 0.15           | -     |

| A2     | 0.031          | 0.051          | 0.80           | 1.05           | -     |

| b      | 0.0075         | 0.0118         | 0.19           | 0.30           | 9     |

| С      | 0.0035         | 0.0079         | 0.09           | 0.20           | -     |

| D      | 0.195          | 0.199          | 4.95           | 5.05           | 3     |

| E1     | 0.169          | 0.177          | 4.30           | 4.50           | 4     |

| е      | 0.026 BSC      |                | 0.65           | BSC            | -     |

| E      | 0.246          | 0.256          | 6.25           | 6.50           | -     |

| L      | 0.0177         | 0.0295         | 0.45           | 0.75           | 6     |

| Ν      | 14             |                | 1              | 4              | 7     |

| α      | 0 <sup>0</sup> | 8 <sup>0</sup> | 0 <sup>0</sup> | 8 <sup>0</sup> | -     |

Rev. 1 6/00

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com